TECHNISCHE

UNIVERSITÄT

WIEN

Vienna University of Technology

# Bachelorarbeit

im

Vertiefungsfach

Technische Elektronik

LV-Nr. 362.094

# Stress Engineering

von

Severin Unger

Matrikel-Nr. 0728168

Eingereicht am

Institut für Festkörperelektronik

TU Wien

Abgabedatum:

14.01.2011

## **Abstract**

Diese Arbeit beschäftigt sich mit Stress-Engineering in MOSFETs.

Im ersten Abschnitt wird das Thema motiviert indem Probleme aufgezeigt werden, die sich bei der sukzessiven Verkleinerung der Gatelängen ergeben. Neben den mechanischen Spannungen, die durch STI (*Shallow Trench Isolation*) entstehen, werden gängige Techniken besprochen, mit denen mechanische Spannung im Kanal bewirkt werden kann. Danach wird ein empirischer und ein einfacher mathematischer Zusammenhang zwischen mechanischer Spannung und Elektronen-Beweglichkeit angegeben.

Der zweite Abschnitt beschäftigt sich mit der Auswertung einer Sentaurus TCAD Simulation, mit der einzelne Prozessschritte nachvollzogen werden können. Den Abschluss bildet eine Gegenüberstellung der Elektronen-Beweglichkeit im fertigen Device mit und ohne Stress-Engineering.

# Inhaltsverzeichnis

|                                                                    |           |

|--------------------------------------------------------------------|-----------|

| <b>1 Einleitung</b>                                                | <b>4</b>  |

| <b>2 Stress-Engineering Technologien</b>                           | <b>4</b>  |

| 2.1 Motivation . . . . .                                           | 4         |

| 2.2 Wichtige Entdeckungen, Early Work . . . . .                    | 6         |

| 2.3 Zusammenhang zwischen mech. Spannung und e-Mobilität . . . . . | 6         |

| 2.4 Wie erreicht man Stress im Kanal? . . . . .                    | 7         |

| 2.4.1 Global: Si über $\text{Si}_{1-x}\text{Ge}_x$ . . . . .       | 8         |

| 2.4.2 Global: Post processing . . . . .                            | 8         |

| 2.4.3 Lokal: Selective Epitaxial Growth (SEG) . . . . .            | 9         |

| 2.4.4 Lokal: Contact Etch Stop Liner (CESL) . . . . .              | 11        |

| 2.4.5 Lokal: Stress Memorization Technique (SMT) . . . . .         | 11        |

| 2.4.6 Lokal: Shallow Trench Isolation (STI) . . . . .              | 12        |

| <b>3 Prozess-Simulation mit Sentaurus TCAD</b>                     | <b>13</b> |

| 3.1 Epitaxial Si:C growth . . . . .                                | 13        |

| 3.2 Stress Memorization Technique (SMT) . . . . .                  | 14        |

| 3.3 Dual Stress Liner . . . . .                                    | 15        |

| 3.4 Gegenüberstellung mit ohne Stress-Engineering . . . . .        | 16        |

| <b>4 Zusammenfassung</b>                                           | <b>19</b> |

# 1 Einleitung

Mittels Stress-Engineering wird es möglich die Band Struktur fundamental zu ändern, so dass trotz kleiner werdender Gate-Längen die Elektronen-Beweglichkeit weiter verbessert werden kann. [3, Background on Materials and Devices]

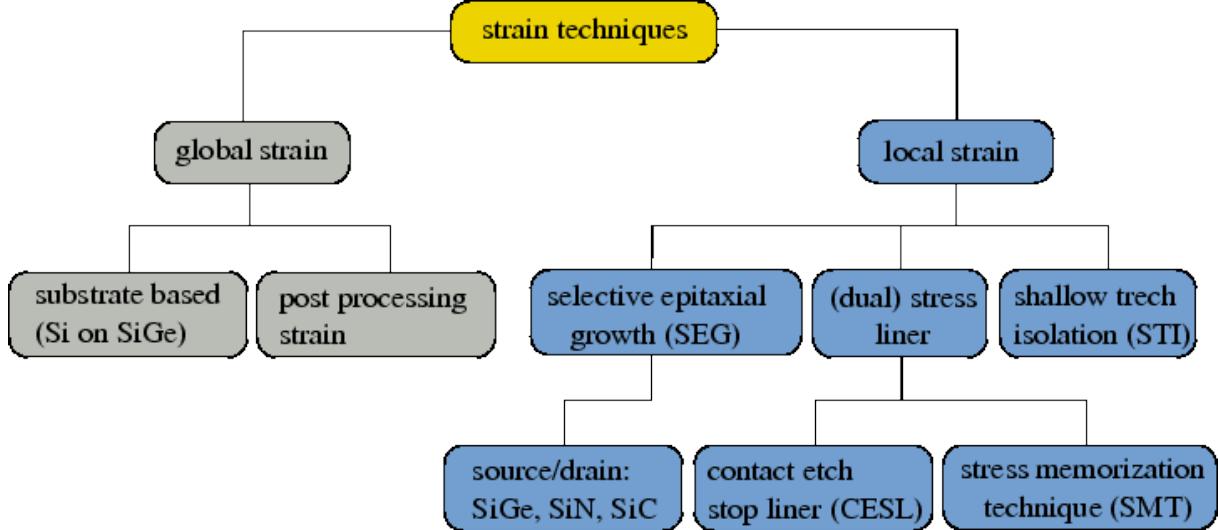

Abbildung 1: Überblick über Stress-Engineering Technologien. [5, Strain Engineering]

Prinzipiell lassen sich die Methoden zur Erreichung von mechanischen Spannungen einteilen in globale, die den ganzen Wafer betreffen, und lokale, die gezielt an bestimmten Stellen am Wafer eingesetzt werden können. Abb. 1 gibt einen Überblick über einige Technologien, die im nächsten Abschnitt genauer besprochen werden.

Wenn CMOS Schaltkreise realisiert werden, wo sowohl n-MOSFETs als auch p-MOSFETs realisiert werden, sind die globalen Methoden nicht anwendbar, weil die beiden Transistor-Arten verschieden auf mechanische Spannungen reagieren. So erreicht man Verbesserungen der Mobilität bei n-MOSFETs mit Zugspannung und bei p-MOSFETs mit Druckspannung. Andersherum würde eine Verschlechterung der Mobilität eintreten. [5, Strain Engineering]

Durch Simulation können die Auswirkungen von Stress-Engineering in den einzelnen Prozessschritten erkannt werden. Im letzten Abschnitt werden mit Sentaurus TCAD einige Prozessschritte nachvollzogen.

## 2 Stress-Engineering Technologien

### 2.1 Motivation

Wenn Si verspannt wird ändert sich die Band-Struktur fundamental, was sich auch auf die Elektronen-Beweglichkeit auswirkt, also salopp gesprochen auf den Kanal-Widerstand.

Mit steigendem  $U_{GS}$  machen sich immer mehr Streueffekte im Kanal bemerkbar, was dafür spricht niedrige  $U_{GS}$  zu verwenden. Doch vor allem in Digital Schaltkreisen sind

hohe  $U_{GT}$  ( $U_{GS} - U_T$ ) erwünscht, weil es sehr hohe Ladungsträger-Dichten hervorruft. [3, First half of 1990]

Steigende elektrische Feldstärke im Kanal geht nach dem Satz vom elektrischen Hüllenfluss mit steigender elektrischer Ladungsdichte einher. Die elektrische Feldstärke im Kanal kann dargestellt werden als

$$E_{surface} = \frac{D_b + D_{inv}}{\varepsilon_0 \varepsilon_r},$$

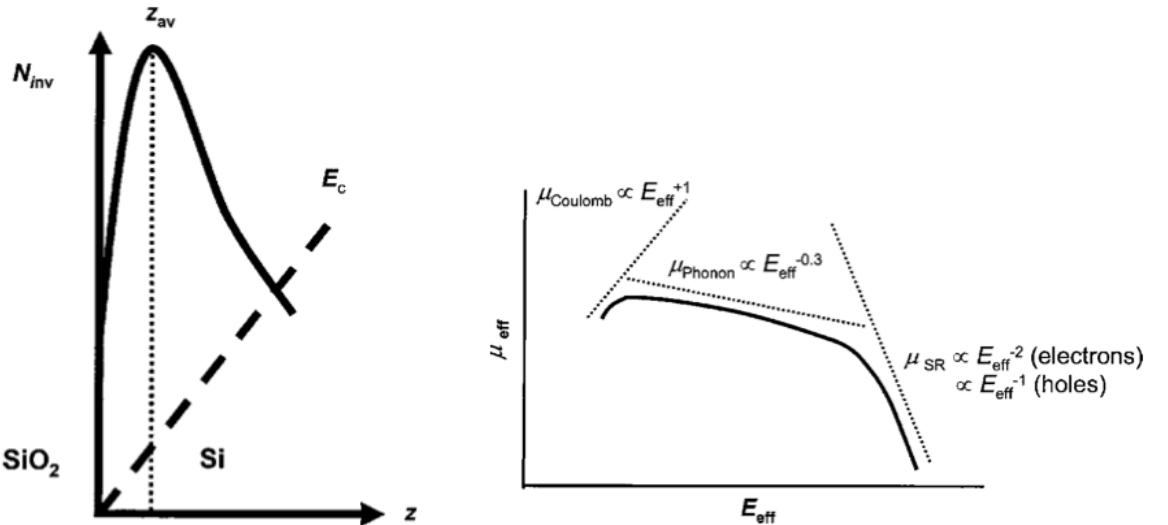

wobei  $D_b$  die Ladungsdichte in der Verarmungszone und  $D_{inv}$  die durch Inversion hervorgerufenen Ladungsdichte bedeutet.  $\varepsilon_r$  ist die relative Dielektrizitätszahl von Silizium. Wegen Quantisierungseffekten an der Oberfläche erfährt der Großteil der Elektronen jedoch eine andere, effektive Feldstärke. Abb. 2 zeigt den Verlauf der Ladungsträgerdichte als Funktion des Abstandes von der Oberfläche. Die Formel für die Feldstärke im Kanal muss also adaptiert werden und man findet

$$E_{eff} = \frac{D_b + \eta D_{inv}}{\varepsilon_0 \varepsilon_r}, \quad (1)$$

wobei der Korrekturfaktor  $\eta$  die Verschiebung knapp unter die Oberfläche berücksichtigt.

Abbildung 2: Verlauf der Teilchendich- Abbildung 3: Streumechanismen als ten als Funktion des Abstandes von der Funktion von  $E_{eff}$ :  $\mu_{Coulomb}$ ,  $\mu_{Phonon}$  Oberfläche. [3, Background on Materi- und  $\mu_{SR}$  (surface roughness). [3, Back- als and Devices] ground on Materials and Devices]

Abb. 3 gibt einen groben Überblick über die Streumechanismen in Abhängigkeit von  $E_{eff}$ . In der Nähe der Threshold Spannung ist die Beweglichkeit am größten, während sie mit steigender Feldstärke zuerst aufgrund von Phononenstreuung und schlussendlich auch aufgrund von Oberflächenstreuung rasant abklingt. Für hohe Elektronen-Beweglichkeiten im Kanal wären also geringe  $E_{eff}$  hilfreich, also solche die sich bei  $U_{gs} \approx U_t$  einstellen.

Doch vor allem in Short-channel-devices ist high-channel-doping notwendig um  $U_T$  einstellen zu können, was aber  $E_{eff}$  wieder vergrößert, wie man in (Gl 1) sieht.

Dieses Problem zeigt, wie wichtig Stress-Engineering für die weitere Entwicklung ist. Mittels Stress-Engineering wird es möglich die Band Struktur fundamental zu ändern, sodass trotz kleiner werdender Gate-Längen die Elektronen-Beweglichkeit weiter verbessert werden kann. [3, Background on Materials and Devices]

## 2.2 Wichtige Entdeckungen, Early Work

| Datum | Struktur                                | Entdeckung/Errungenschaft                                                                                                                                                                                                                                                                                                                                                                   |

|-------|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1984  | SiGe, Si                                | People et al. beobachteten ein 2-dimensionales Elektronen-Gas (2DHG <sup>1</sup> ) in modulation-doped strained-Si <sub>0.8</sub> Ge <sub>0.2</sub> auf Si Substrat. Wegen der unterschiedlichen Band-gaps in Si und Ge kommt es zur Biegung des Valenzbandes (type I <sup>2</sup> ), wodurch neben der Elektronen-Diffusion auch eine Änderung der Elektronenmobilität hervorgerufen wird. |

| 1985  | Si, SiGe                                | Wenn Si auf entspanntes SiGe gewachsen wird entsteht ein type II band.                                                                                                                                                                                                                                                                                                                      |

| 1991  | SiGe                                    | Ein relaxed graded buffer mit geringen Störungen (Versetzungen im Gitter von 10 <sup>8</sup> auf 10 <sup>6</sup> minimiert).                                                                                                                                                                                                                                                                |

| 1992  | SiGe, Si, SiGe                          | Ein Si-Kanal wird zwischen zwei SiGe-Kanälen "vergraben". Buried-channel Devices (vergrabener Kanal) zeigten bessere $\mu$ als surface-channel Devices. Bei großen $U_{GT}$ war der Vorteil verflogen, weil Elektronen aus dem Kanal herausgezogen werden.                                                                                                                                  |

| 1993  | Si, Si <sub>0.4</sub> Ge <sub>0.6</sub> | Ein 2DHG wurde beobachtet. Ein neuer Maximalwert für $\mu = 55000 \text{ cm}^2/(\text{Vs})$ wurde erreicht.                                                                                                                                                                                                                                                                                 |

Tabelle 1: Wichtige Entdeckungen/Errungenschaften, cronologisch. [3, Early Work]

## 2.3 Zusammenhang zwischen mech. Spannung und e-Mobilität

Deformation induziert mechanische Verspannung und führt zum Piezoresistiven Effekt. [6, Introduction]

Unter der Voraussetzung, dass die Änderung der Schwellenspannung mit der mechanischen Verspannung vernachlässigbar ist, ist die relative Änderung der e-Mobilität durch

$$\frac{\Delta \mu_{eff}}{\mu_{eff}} = \pi \cdot \sigma$$

gegeben, wobei  $\sigma$  der Spannungstensor ist und  $\pi$  die Sensitivität der Drain-Mobilität aufgrund der Verspannung angibt, also den *Piezoresistiven Koeffizienten*. [6, Experiments, The Mobility parameter U0], [4]

---

<sup>1</sup>In einem 2DEG (2-dimensional Electron Gas) oder 2DHG (2-dimensional Hole Gas) weisen 4 der 6 ⟨100⟩ -Richtungen eine weitaus höhere Beweglichkeit auf als die anderen beiden. Daraus resultiert, dass sich die Elektronen/Löcher scheinbar ausschließlich innerhalb den 4 bevorzugten Richtungen bewegen. [3, Strained Si n-MOSFETs]

<sup>2</sup>Type I, *Straddling Gap*:  $E_{C,1} < E_{C,2}$  und  $E_{V,1} > E_{V,2}$ . [7]

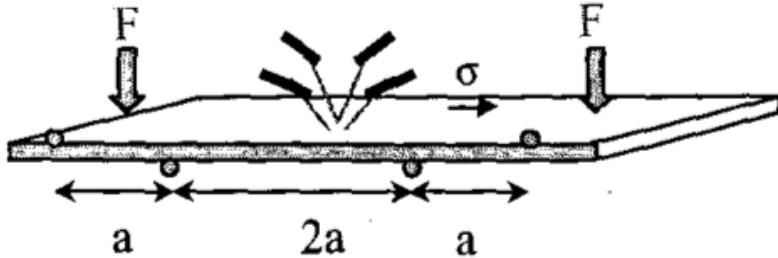

Gallon und Andere [2] haben in einem Experiment den Zusammenhang zwischen mechanischer Verspannung und Elektronen-Mobilität ermittelt. Ein rechteckig zugeschnittener Wafer wurde mit der 4-Punkt-Biege Methode gewölbt, sodass an der Waferoberfläche eine Zugspannung entsteht (Abb. 4). [2, Experimental Method]

Abbildung 4: 4-Punkt-Biege Methode [2, Experimental Method]

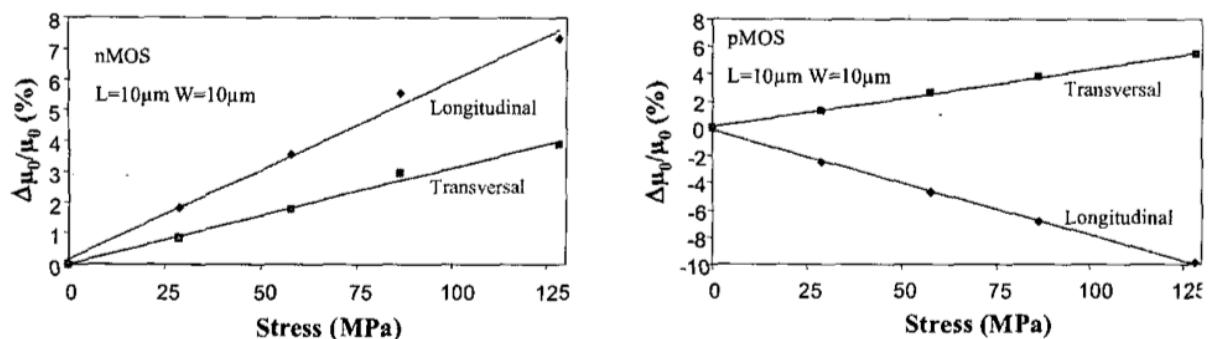

Die Änderung von  $\frac{\Delta\mu_0}{\mu_0}$  mit der Zugspannung ist in Abb. 5 für nMOS und pMOSFETs dargestellt.

Abbildung 5: Normalisierte Änderung der Mobilität über der mechanischen Verspannung. [2, Experimental results]

Man sieht in Abb. 5 eine bemerkenswert lineare Abhängigkeit.

Man sieht außerdem, dass die e-Mobilität in nMOSFETs sowohl mit zunehmender lateraler Zugspannung als auch mit zunehmender longitudinal Zugspannung größer wird. pMOSFETs zeigen bei transversaler Zugspannung ein ähnliches Verhalten, bei longitudinaler Zugspannung wird die e-Mobilität allerdings kleiner.

## 2.4 Wie erreicht man Stress im Kanal?

Enzo Ungersböck hat in seiner Dissertation an der Technischen Universität Wien eine Kategorisierung der wichtigsten Methoden getroffen. Abb. 1 zeigt diese Einteilung. Prinzipiell wird zwischen Methoden zur globalen und lokalen Erzeugung von Strain unterschieden.

Bei den globalen Methoden gibt es zwei Herangehensweisen. Entweder der Strain wird durch das Substrat bestimmt (substrate based strain), oder der Strain wird im Nachhinein auf der Oberfläche induziert (post processing strain). Die lokalen Verfahren bieten im

Gegensatz zu den globalen die Möglichkeit sowohl n-MOS als auch p-MOS -FETs auf dem selben Wafer zu realisieren. Die vier in der Literatur am häufigsten genannten sind in Abb. 1 angeführt.

Bei der *Selective Epitaxial Growth (SEG)* Technik und *Contact Etch Stop Liner (CESL)* Technik bewirkt die aufgetragene Substanz den gewünschten Effekt.

Bei *Stress Memorization Technique (SMT)* überträgt die aufgetragene Substanz eine mechanische Spannung an die Oberfläche und wird anschließend wieder entfernt. [5, Stress Memorization]

Eine Verspannung zufolge von *Sahllow Trench Isolation (STI)* wird durch die Grabe-nisationen bewirkt. [5, Stress from Shallow Trench Isolation]

Die in Abb. 1 angeführten Verfahren sollen in weiterer Folge näher beschrieben werden.

#### 2.4.1 Global: Si über $\text{Si}_{1-x}\text{Ge}_x$

Durch die unterschiedlichen Gitterkonstanten tritt eine mechanische Verspannung der Si-Schicht auf. Erst seit 1991, als die Herstellung eines relaxed, graded buffers mit ausreichender Präzision möglich war, hat dieses Verfahren merkbare Verbesserungen gegenüber Bulk-Si gezeigt. [3, Advent of relaxed graded buffer]

**Ge-Gehalt im Virtual Substrate** Der wichtigste bestimmende Faktor ist der Ge-Gehalt im Virtual Substrate. Denn dieser bestimmt den Grad der Verspannung und damit die Aufteilung in  $\Delta_2$  und  $\Delta_4$  valleys. Experimentell hat sich herausgestellt, dass die Beweglichkeit bis  $\approx 0.8\%$  monoton mit der zweiachsigen Verspannung wächst. [3, Long-channel strained-Si n-MOSFETs, Effect of strain]

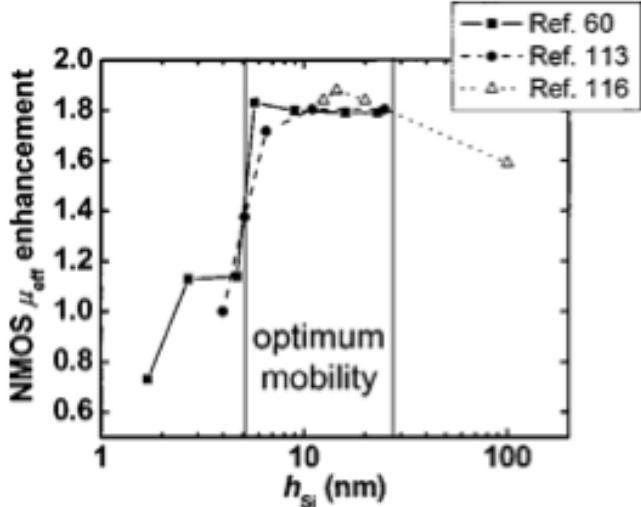

**Die verspannte Si-Schicht sollte  $\approx 6 \text{ nm}$  haben** Es hat sich gezeigt, dass die Beweglichkeits-Verbesserung verschwindet, wenn die Dicke  $< 6 \text{ nm}$  gewählt wird. Für Schichten dicker als 6 nm zeigt sich eine verschwindende Abhängigkeit der Beweglichkeit von der Schichtdicke. In Abb. 6 ist der optimale Bereich, in dem sich die Dicke befinden sollte, dargestellt. [3, Effect of e-Si thickness]

Wenn man identisch hergestellte Bulk-Si und  $\text{Si}_{1-x}\text{Ge}_x$ -Si n-MOSFETs vergleicht, zeigt sich, dass die Schwellspannung  $U_T$  in Strained-Si devices typischerweise 100 bis 200 meV unter der von Bulk-Si devices liegt. Der Grund dafür ist der Leitungsband-Offset an der Oberfläche. [3, C Short-channel strained-Si n-MOSFETs, Compensation for conduction-band offset]

#### 2.4.2 Global: Post processing

Diese Verfahren beginnt erst nachdem der herkömmliche Fertigungsprozess des Wafers vollständig abgeschlossen ist. Der fertige Wafer wird auf eine Dicke von  $\approx 10 \text{ um}$  präpariert und anschließend auf eine Polymer Schicht übertragen. Innerhalb der elastischen Grenzen kann der Wafer dann beliebig verzerrt werden, wobei sowohl uniaxiale als auch biaxiale Verzerrungen bewirkt werden können. [5, Post Processing]

Ein großer Vorteil dieser Heransgehensweise, um mechanische Spannungen zu erzeugen, ist der, dass die Herstellung ohne Rücksichtnahme auf Stress Engineering in herkömmlicher Weise erfolgen kann. Nachteilig ist, dass n- und p-MOSFET nicht getrennt behandelt werden können. [5, Post Processing]

Abbildung 6: Die optimale Schichtdicke der verspannten Si-Schicht auf dem  $\text{Si}_{1-x}\text{Ge}_x$  Wafer. [3, Effect of e-Si thickness]

Verbesserungen gegenüber unverspannten Strukturen, die mit dieser Methode erzielt wurden, zeigt (Tab 2).

n-MOSFET: 18.05%

p-MOSFET: 14.56%

Tabelle 2: Verbesserungen durch Post Processing gegenüber entspanntem Bulk-Si. [5, Post Processing]

#### 2.4.3 Lokal: Selective Epitaxial Growth (SEG)

Bei dieser Technik wird uniaxialer mechanische Verspannung im Kanal bewirkt, indem die Source/Drain Gebiete (wahlweise) mit  $\text{Si}_{1-x}\text{C}_x$  oder  $\text{Si}_{1-x}\text{Ge}_x$  aufgebaut werden, je nachdem ob es sich um einen nMOS (Zugspannung) oder einen pMOS handelt (Kompression). Die gewünschte Verspannung im Kanal kommt dadurch zustande, dass die Gitterkonstanten von  $\text{Si}_{1-x}\text{C}_x$  und  $\text{Si}_{1-x}\text{Ge}_x$  nicht mit der Gitterkonstanten von Si übereinstimmen. Gute Ergebnisse wurden erzielt mit  $\text{Si}_{0.99}\text{C}_{0.01}$  und  $\text{Si}_{0.75}\text{Ge}_{0.25}$ , um spezielle Werte für  $x$  zu nennen. [5, Selective Epitaxial Growth Technique]

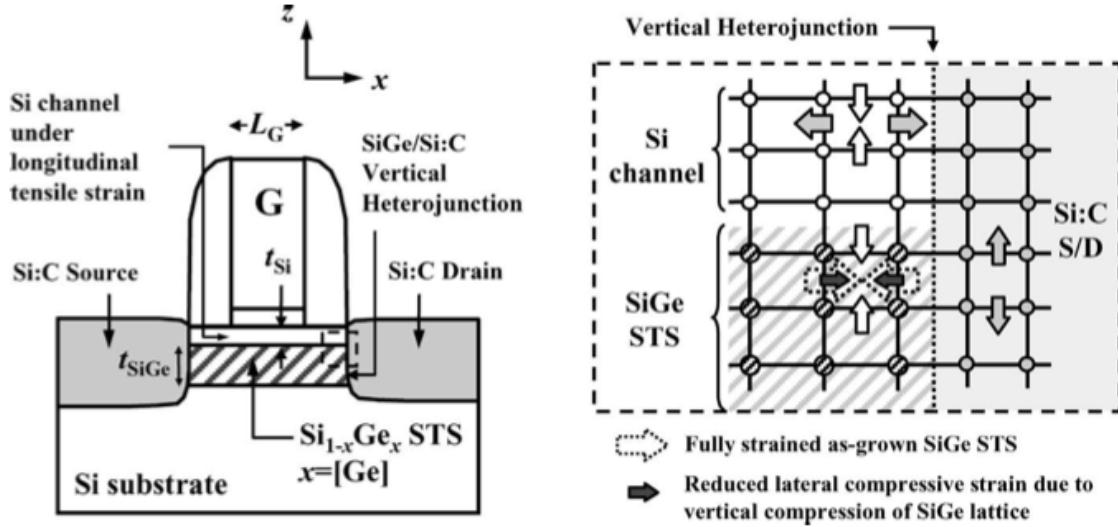

In einem Paper [1] wurde, mittels Simulationen festgestellt, berichtet, dass die Performance von MOSFET Bauelementen weiter gesteigert werden kann, wenn zusätzlich unter dem Kanal eine sogenannte *Strain Transfer Structure (STS)* eingebaut wird, die die Verspannung an den Kanal weitergibt. Abb. 9 zeigt den Aufbau des MOSFET. Unter dem Kanal befindet sich die *Strain Transfer Structure (STS)* aus  $\text{Si}_{1-x}\text{Ge}_x$ . Darauf befindet sich die Si-Schicht, die wegen der unterschiedlichen Gitterkonstanten an der Grenzfläche mechanisch verspannt wird. Die Source/Drain Gebiete werden jetzt mit Kohlenstoff dotiert, sodass sich die Gitterkonstanten gegenüber der von SiGe noch weiter absenkt, als sie

ohnehin schon ist. Die STS wird jetzt also vertikal an den Grenzflächen zu Source/Drain verspannt, wodurch sich die Druckspannung in Kanalrichtung vermindert (Inset von Abb 9). Diese vermindernde Druckspannung äußert sich schlussendlich als eine Zugspannung in der darüberliegenden Si-Schicht. Eine mit Finiten Elementen Methoden erstellte Auswertung der so entstandenen Struktur ist in Abb. 8 dargestellt. Diese Auswertung macht deutlich, wie sich eine vertikale Verzerrung der STS Abb. 8a als eine laterale Verzerrung im darüberliegenden Si-Kanal Abb. 8b äußert. [1, Device Design]

Abbildung 7: Aufbau der MOSFET-Struktur mit STS und Si:C. [1, Device Design]

Abbildung 8: Numerische Auswertung der MOSFET-Struktur mit STS und Si:C. Dargestellt sind die Längenänderungen in %. [1, Device Design]

Verbesserungen gegenüber unverspannten Strukturen, die mit dieser Methode erzielt wurden, zeigt Tab 3.

n-MOSFET: 18%

p-MOSFET: –

Tabelle 3: Verbesserungen durch Si:C und STS gegenüber entspanntem Bulk-Si. [1, Abstract]

#### 2.4.4 Lokal: Contact Etch Stop Liner (CESL)

Bei dieser Technik wird eine hochgradig verspannte Mantelschicht ("Liner") gleichförmig auf der Waferoberfläche abgeschieden. Dieser Vorgang beginnt erst nach Abschluss des Silicid Vorgangs. Die Verspannung der aufgetragenen Schicht überträgt sich teilweise auf die darunterliegende Struktur. Wie stark die Oberfläche tatsächlich verspannt wird hängt von den Materialeigenschaften der abgeschiedenen Schicht ab und kann unter anderem durch deren Dicke beeinflusst werden.

Da sich die Leitfähigkeit in n-MOSFETs durch Zugspannung und in p-MOSFETs durch Kompression verbessert, sind je nach Bauelement verschiedene Schichten („Liner“) zu verwenden. Wenn beide MOSFET-Typen vorhanden sind, wenn also 2 verschiedene „Liner“ verwendet werden müssen, dann spricht man vom „Dual-stress-liner“ Verfahren, ansonsten nur vom „stress-liner“ Verfahren. [5, Contact Etch Stop Liner]

Verbesserungen gegenüber unverspannten Strukturen, die mit dieser Methode erzielt wurden, zeigt (Tab 4).

n-MOSFET: 11%

p-MOSFET: 20%

Tabelle 4: Verbesserungen durch Contact Etch Stop Liner (CESL) gegenüber entspanntem Bulk-Si. [5, Contact Etch Stop Liner]

#### 2.4.5 Lokal: Stress Memorization Technique (SMT)

Bei diesem Verfahren wird eine verspannte Nitrid-Schicht auf dem Wafer abgeschieden. Anschließend wird das Spike-Anneal Verfahren durchgeführt, wodurch sich die Verspannung bei der Rekristallisation auf die Oberfläche des Wafers überträgt. Noch bevor mit dem Salicide Prozess begonnen wird, wird die verspannte Nitrid-Schicht schrittweise wieder entfernt. Die Verspannung an der Oberfläche geht dabei, wegen der vorangegangenen Rekristallisation nicht verloren. [5, Stress Memorization]

Ein entscheidender Vorteil dieses Verfahrens ist, dass während der Fabrikation nicht auf das Stress Engineering und die dabei verwendeten Materialen Rücksicht genommen werden muss, da die entsprechenden Schichten vor Beginn der eigentlich Fabrikation wieder entfernt werden. [5, Global Strain Techniques]

n-MOSFET: 15%

p-MOSFET: –

Tabelle 5: Verbesserungen durch Stress Memorization gegenüber entspanntem Bulk-Si. [5, Stress Memorization]

#### 2.4.6 Lokal: Shallow Trench Isolation (STI)

Zwischen den Bauelementen ist bekanntlich eine Isolation notwendig, um die Bauelemente voneinander abzugrenzen. Dafür wird ein Graben verwendet (shallow trench).

Bei den immer kleiner werdenden Technologien kann die induzierte mechanische Spannung, die durch die Grabenisolationen bewirkt wird, nicht mehr vernachlässigt werden. Der Kanal wird zunehmend komprimiert (compressive stress). Dabei wird die Mobilität in pMOSFETs zunehmend größer während sie in nMOSFETs zunehmend geringer wird. [2, Stress induced by STI]

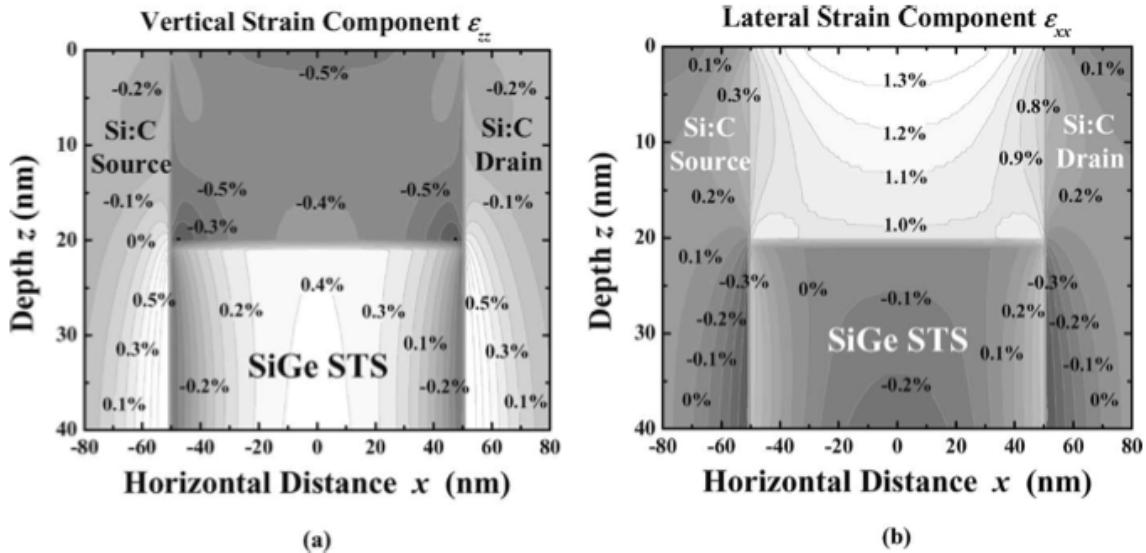

Abbildung 9: Schematische Darstellung von mechanischen Verspannungen, durch STI induziert. [2, Stress induced by STI]

Je größer der Parameter  $a$  ist desto schwächer wird die mechanische Kompression  $\sigma$ . Der Zusammenhang zwischen  $a$  und  $\sigma$  kann durch

$$\sigma(a) = \sigma(a_{min}) \left[ 1 + K_\sigma \left( \frac{a - a_{min}}{a} \right) \right]$$

beschrieben werden. Dabei sind  $K_\sigma$  und  $a_{min}$  passende Parameter und  $\sigma(a_{min})$  eine Referenz-Verspannung bei  $a_{min}$ . [2, Stress induced by STI]

Mit der richtigen Kombination von *Selective Epitaxial Growth (STI)* und *Contact Etch Stop Liner (CESL)* kann für nMOSFETs dennoch eine Zugspannung im Kanal erreicht werden. [5, Stress from Shallow Trench Isolation]

### 3 Prozess-Simulation mit Sentaurus TCAD

Die Sentaurus-Vorlage enthält einen kompletten Prozessablauf zur Herstellung sowohl von nMOS als auch von pMOSFETs. Die Ausführungen in diesem Abschnitt beschränken sich auf die Herstellung von nMOSFETs.

Bei den Auswertungen werden immer sowohl vertikale als auch laterale mechanische Verspannung beachtet.

In diesem Prozess werden alle 4 in dieser Arbeit genannten lokalen Stress-Engineering-Technologien angewendet bzw. berücksichtigt. Der Herstellungsprozess gliedert sich in 5 Abschnitte:

- **Isolation:** Hier kommen die Auswirkungen der *Shallow Trench Isolation (STI)* ins Spiel.

- Poly

- **Extensions:** Hier werden in den Source/Drain Gebieten tiefe Gräben geätzt, die anschließend epitaktisch mit Kohlenstoff-dotiertem Silizium wieder gefüllt werden (*Epitaxial Si:C growth*).

- **SD:** Hier wird mit einer Temperaturbehandlung die mechanische Spannung eines Heatabsorbers auf den Wafer übertragen (*Stress Memorization*).

- **Salicide:** Hier wird Oxynitrid auf dem Wafer abgeschieden, um dessen Oberfläche zu verspannen (*Dual Stress Liner*).

- DeviceMesh

Für eine detaillierte Erklärung des gesamten Prozessablaufs sei auf die Bachelorarbeit *32nm CMOS-Technologie* verwiesen.

#### 3.1 Epitaxial Si:C growth

Die Kohlenstoff-dotierten Source/Drain Gebiete werden in mehreren Prozessschritten durch Epitaxie hergestellt. Das Ergebnis der Auswertungen ist ähnlich wie in Abschnitt 2.4.3, jedoch hier ohne einer *Strain Transfer Structure*.

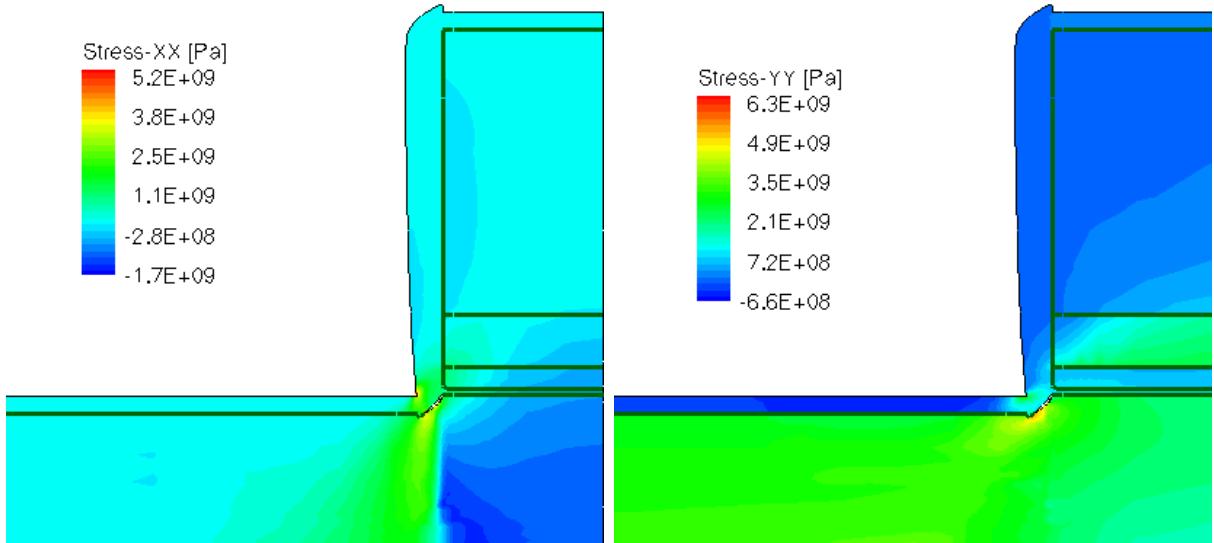

In Abb. 10 ist die vertikale, resultierende, mechanische Spannung farblich dargestellt. An der Grenzfläche zwischen Drain und Kanal kommt es aufgrund der unterschiedlichen Gitterkonstanten von  $\text{Si}_{1-x}\text{Ge}_x$  (Drain) und Si (Kanal) zu einer vertikalen Verspannung. Im Drain-Bereich wirken Zugspannungen (Grün  $\approx 10^9 \text{ Pa}$ ), im Kanal-Bereich wirkt kompressiver Druck (Blau  $\approx -10^9 \text{ Pa}$ ).

Abb. 11 zeigt wieder die selbe Situation, diesmal aber die lateralen, resultierenden, mechanischen Spannungen. Die vertikale Kompression im Kanal-Bereich aus Abb. 10 bewirkt hier jetzt eine laterale Zugspannung (Grün  $\approx 10^9 \text{ Pa}$ ).

Abbildung 10: Vertikale Verspannung in der Abbildung 11: Laterale Verspannung in der MOS Struktur (Drain+halber Kanal) mit MOS Struktur (Drain+halber Kanal) mit Stress-Engineering.

### 3.2 Stress Memorization Technique (SMT)

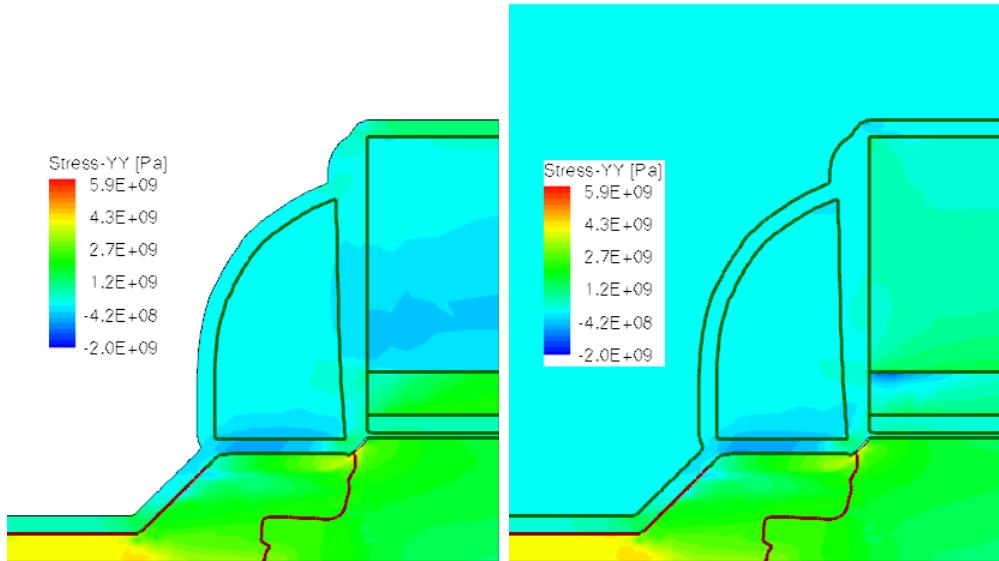

Sentaurus TCAD benützt für die Simulation von *SMT* ein elastoplastisches und ein visco-elastisches Modell. Abb. 12 zeigt die mechanische Spannungsverteilung der MOS Struktur vor Beginn des Prozesses. Der Betrag und das Vorzeichen der mechanischen Spannung sind farblich dargestellt. Dunkelblau bedeutet hohe Kompression ( $\approx -2 \cdot 10^9$  Pa), Grif-grün bedeutet ebenso große Zugspannung ( $\approx 2 \cdot 10^9$  Pa). Der Stress, der übertragen werden soll, wird im aufgetragenen Heatabsorber eingestellt, Abb. 13.

Abbildung 12: Lateraler Stress in der Abbildung 13: Lateraler Stress in MOS Struktur (nur Drain) vor dem der MOS Struktur (nur Drain) mit SMT Prozess.

Abbildung 13: Lateraler Stress in MOS Struktur (nur Drain) mit Heatabsorber.

Anschließend beginnt eine drei-stufige Temperaturbehandlung um die Verspannung auf die MOS Struktur zu übertragen. Dabei wird die Temperatur von  $600\text{ }^{\circ}\text{C}$  auf  $950\text{ }^{\circ}\text{C}$  gesteigert, Abb. 14. Nach Entfernung des Heatabsorbers bleibt die Verspannung zurück, der SMT Vorgang ist abgeschlossen, Abb. 15.

Abbildung 14: Lateraler Stress in der Abbildung 15: Lateraler Stress in der MOS Struktur (nur Drain) nach der MOS Struktur (nur Drain) nach Fertigstellung des SMT Prozesses.

### 3.3 Dual Stress Liner

Das Dual Stress Liner Verfahren beginnt erst nach Beendigung des Silicid Vorgangs.

Mechanisch verspanntes Oxynitrid wird auf der Waferoberfläche isotrop abgeschieden. Dabei entsteht auf der Oberfläche isotrope Zugspannung.

### 3.4 Gegenüberstellung mit ohne Stress-Engineering

Im Folgenden werden die Fakten und Eigenschaften des fertigen Bauelements mit und ohne Stress-Engineering gegenübergestellt. Zuerst betrachten wir die mechanische Verspannungen und dann die Elektronenmobilität.

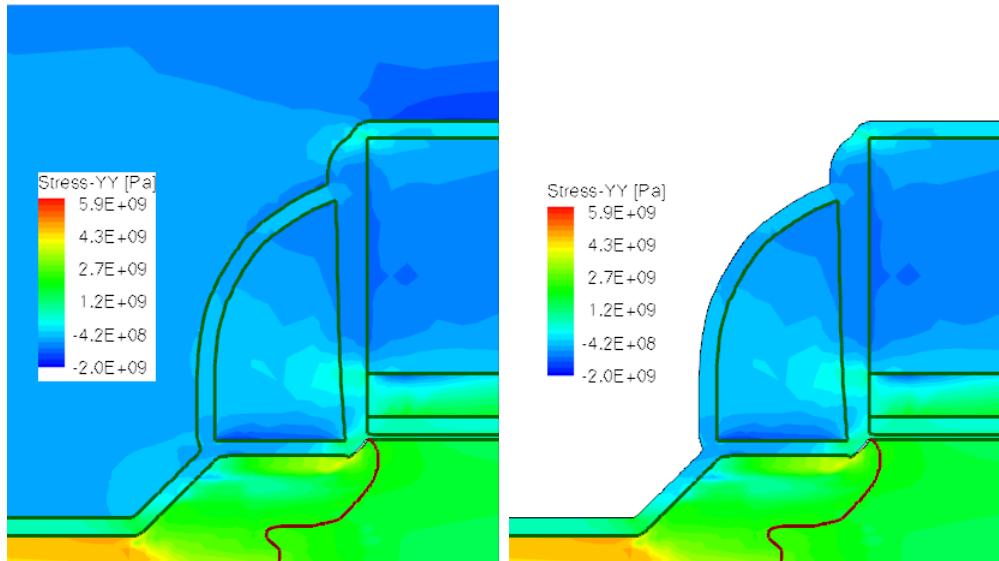

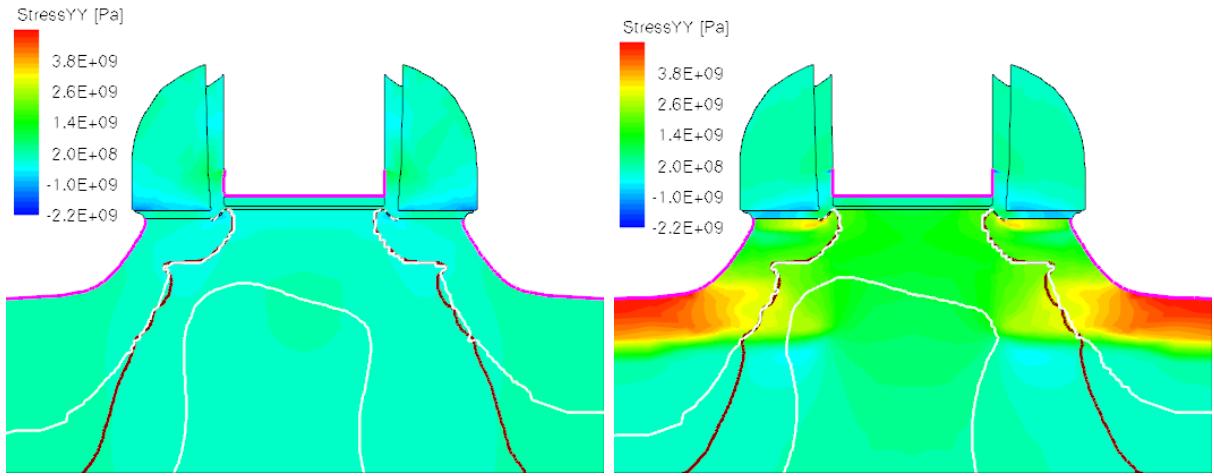

Die mechanische Verspannung mit und ohne Stress-Engineering ist jeweils in Abb. 16 und Abb. 17 dargestellt. Mit Stress-Engineering wirkt die Kompression (Blau  $\approx -10^9$  Pa) gleichmäßig im Kanal, während sie ohne Stress-Engineering nur in der Mitte konzentriert ist und zu den Rändern hin stark abnimmt.

Abbildung 16: Vertikale Verspannung ohne

Abbildung 17: Vertikale Verspannung mit

Stress-Engineering. Stress-Engineering.

Noch deutlicher sieht man die Auswirkungen an den lateralen Zugspannungen im Kanal, die jeweils in Abb. 18 und Abb. 19 dargestellt sind. Während sich ohne Stress-Engineering lediglich  $\approx 10^8$  Pa einstellen sind es mit Stress-Engineering  $\approx 10^9$  Pa.

Abbildung 18: Laterale Verspannung ohne Abbildung Stress-Engineering.

Abbildung 19: Laterale Verspannung mit Stress-Engineering.

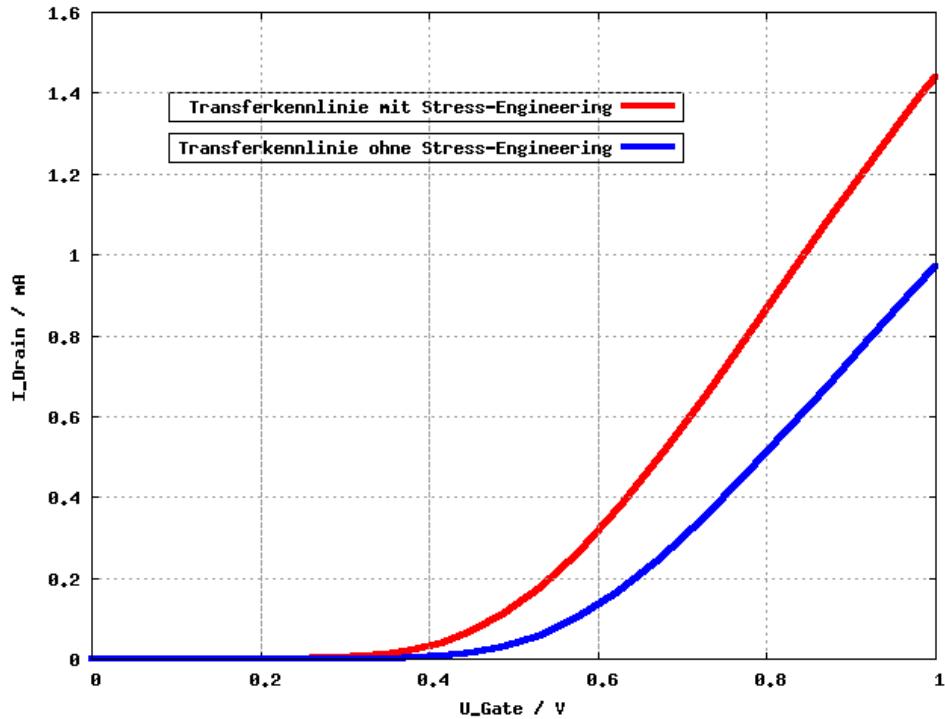

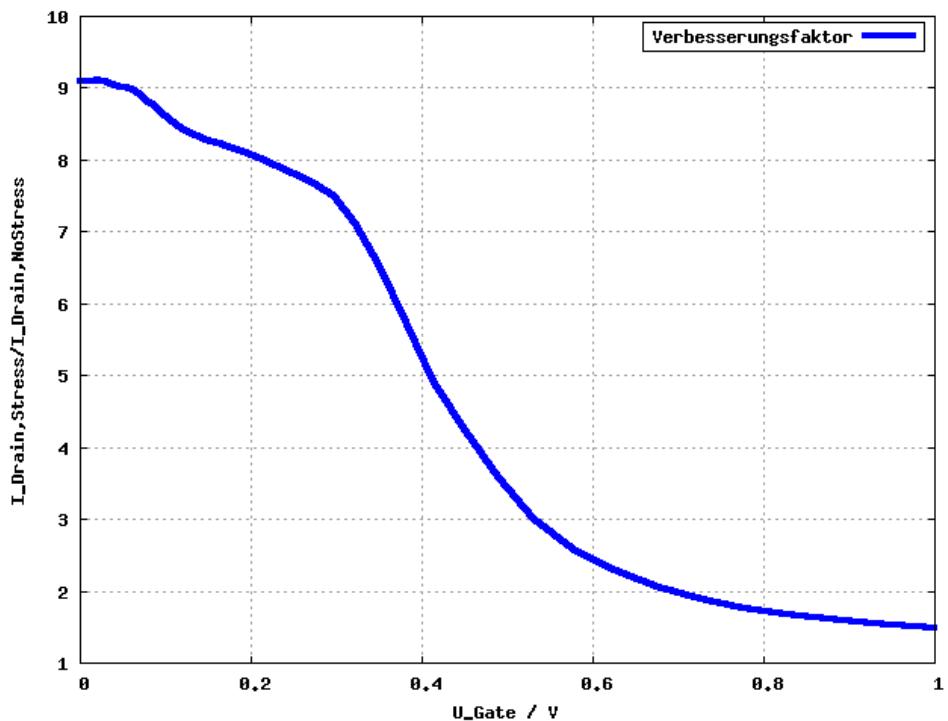

Schlussendlich soll der Strom im Kanal betrachtet werden. Abb. 20 zeigt den Drain-Strom (y-Achse) sowohl mit als auch ohne Stress-Engineering als Funktion der Gate-Spannung (x-Achse). Dabei beträgt die Drain-Spannung  $U_{Drain} = 1V$ . Der Faktor, um den sich die beiden Kurven unterscheiden, ist in Abb. 21 dargestellt.

Abbildung 20: Transferkennlinien mit und ohne Stress-Engineering bei  $U_{Drain} = 1V$ .

Abbildung 21: Quotient der Drain-Ströme  $\frac{\text{mit}}{\text{ohne}}$  Stress-Engineering.

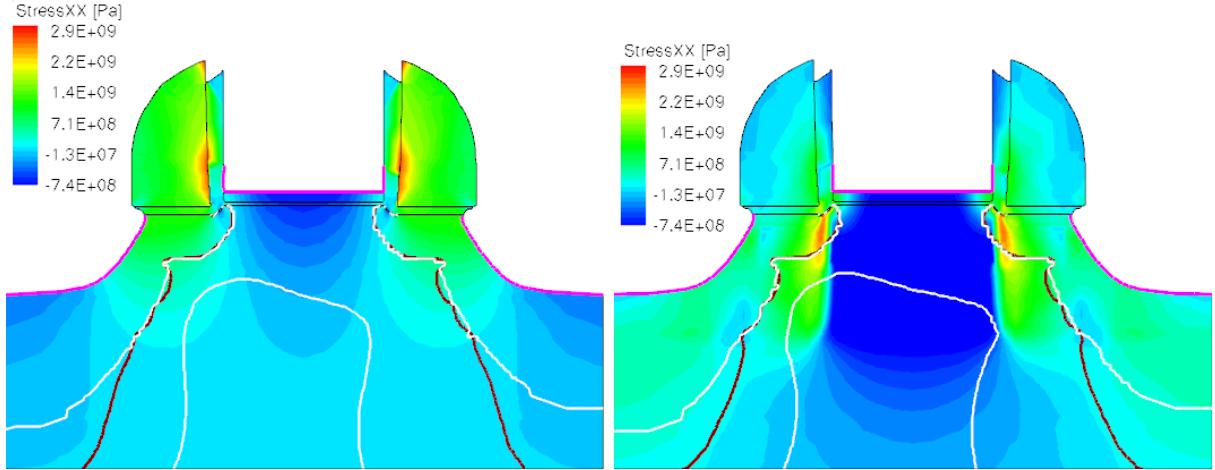

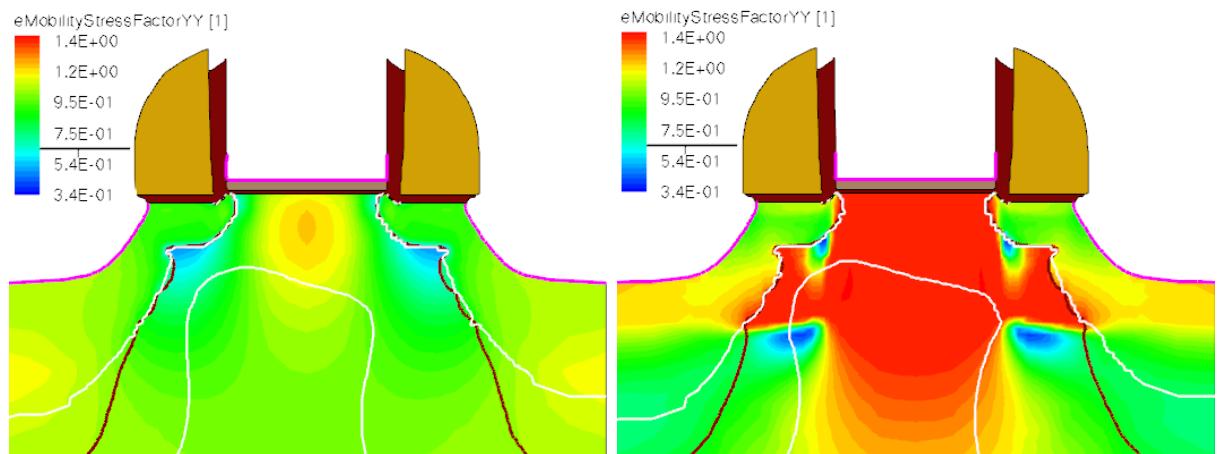

Abbildung 22: Faktor, um den sich Elektronen-Mobilität durch mechanische Verspannung geändert hat, ohne Stress-Engineering.

Abbildung 23: Faktor, um den sich Elektronen-Mobilität durch mechanische Verspannung geändert hat, mit Stress-Engineering.

Abb. 22 und Abb. 23 zeigen jeweils ohne und mit Stress-Engineering den Faktor, um den sich die Elektronen-Mobilität aufgrund mechanischer Verspannung geändert hat.

## 4 Zusammenfassung

Bei immer kleiner werdenden Strukturen können Verspannungen in der Struktur (z.b. von STI hervorgerufen) bei der Analyse und Simulation nicht mehr außer Acht gelassen werden. Mit Stress-Engineering kann die Band-Struktur grundlegend beeinflusst werden. Damit kann parasitäre Verspannungen entgegengewirkt und die Elektronen-Beweglichkeit sogar gesteigert werden.

In den 1980er Jahren wurden einige Schlüssel-Entdeckungen in der Bandstruktur von SiGe Heterostrukturen gemacht. Heute wird von mehreren Verfahren berichtet. Es gibt globale Techniken, die auf dem ganzen Wafer gleichzeitig wirken (Si on SiGe, Post Processing), und lokale Techniken, mit denen auch nMOS und pMOSFETs auf dem selben Wafer gezielt manipuliert werden können (SEG, DSL, SMT).

Experimente zeigen in guter Näherung einen linearen Zusammenhang zwischen mechanischer Verspannung und Elektronen-Mobilität. Dabei steigt bei lateraler Zugspannung die Mobilität in nMOSFETs, während sie in pMOSFETs sinkt. Umgekehrt sinkt bei lateraler Kompression die Mobilität in nMOSFETs, während sie in pMOSFETs steigt.

In der Sentaurus TCAD (Synopsys) Simulation wird die laterale Spannung nach den einzelnen Prozessschritten sichtbar gemacht. Beim fertigen Device ist im Kanal ein Elektron-Mobility-Stress-Faktor von  $\approx 1.4$  feststellbar, also eine Mobilitäts-Verbesserung von  $\approx 40\%$  durch Stress-Engineering.

## Literatur

- [1] Kah-Wee Ang, Jianqiang Lin, Chih-Hang Tung, Narayanan Balasubramanian, Ganesh S. Samudra, and Yee-Chia Yeo. Strained n-MOSFET with embedded source/drain stressors and strain-transfer structure (STS) for enhanced transistor performance. *IEEE Transactions on Electron Devices*, 55:850–857, 2008.

- [2] C. Gallon, G. Reimbold, G. Ghibaudo, R.A. Bianchi, R. Gwoiecki, and C. Raynaud. Electrical analysis of mechanical stress induced by shallow trench isolation. In *European Solid-State Device Research, 2003*, pages 359 – 362, 2003.

- [3] Minjoo L. Lee, Eugene A. Fitzgerald, Mayank T. Bulsara, Matthew T. Currie, and Anthony Lochtefeld. Strained si, sige, and ge channels for high-mobility metal-oxide-semiconductor field-effect transistors. *Journal of Applied Physics*, 97:011101–011101–28, 2005.

- [4] Synopsys. *Sentaurus Device User Guide, Chapter 27, Modeling Mechanical Stress Effect*, March 2010. version D-2010.03.

- [5] Enzo Ungersboeck. *Advanced Modeling of Strained CMOS Technology*. PhD thesis, Technischen Universität Wien, 2007.

- [6] N. Wacker, M.-U. Hassan, H. Richter, H. Rempp, and J.N. Burghartz. Compact modeling of cmos transistors under uniaxial stress. In *12th Annual Workshop on Semiconductor Advances for Future Electronics and Sensors (SAFE)*, pages 179–181, 2009.

- [7] Wikipedia. Heterojunction types. <http://en.wikipedia.org/wiki/Heterojunction>. downloaded at 2011-01-17.

# Abbildungsverzeichnis

|    |                                                                                                                                                            |    |

|----|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1  | Überblick über Stress-Engineering Technologien. [5, Strain Engineering]                                                                                    | 4  |

| 2  | Verlauf der Teilchendichten als Funktion des Abstandes von der Oberfläche. [3, Background on Materials and Devices]                                        | 5  |

| 3  | Streumechanismen als Funktion von $E_{eff}$ : $\mu_{Colomb}$ , $\mu_{Phonon}$ und $\mu_{SR}$ (surface roughness). [3, Background on Materials and Devices] | 5  |

| 4  | 4-Punkt-Biege Methode [2, Experimental Method]                                                                                                             | 7  |

| 5  | Normalisierte Änderung der Mobilität über der mechanischen Verspannung. [2, Experimental results]                                                          | 7  |

| 6  | Die optimale Schichtdicke der verspannten Si-Schicht auf dem $Si_{1-x}Ge_x$ Wafer. [3, Effect of e-Si thickness]                                           | 9  |

| 7  | Aufbau der MOSFET-Struktur mit STS und Si:C. [1, Device Design]                                                                                            | 10 |

| 8  | Numerische Auswertung der MOSFET-Struktur mit STS und Si:C. Dargestellt sind die Längenänderungen in %. [1, Device Design]                                 | 10 |

| 9  | Schematische Darstellung von mechanischen Verspannungen, durch STI induziert. [2, Stress induced by STI]                                                   | 12 |

| 10 | Vertikale Verspannung in der MOS Struktur (Drain+halber Kanal) mit Stress-Engineering.                                                                     | 14 |

| 11 | Laterale Verspannung in der MOS Struktur (Drain+halber Kanal) mit Stress-Engineering.                                                                      | 14 |

| 12 | Lateraler Stress in der MOS Struktur (nur Drain) vor dem SMT Prozess.                                                                                      | 15 |

| 13 | Lateraler Stress in der MOS Struktur (nur Drain) mit Heatabsorber.                                                                                         | 15 |

| 14 | Lateraler Stress in der MOS Struktur (nur Drain) nach der Temperaturbehandlung.                                                                            | 15 |

| 15 | Lateraler Stress in der MOS Struktur (nur Drain) nach Fertigstellung des SMT Prozesses.                                                                    | 15 |

| 16 | Vertikale Verspannung ohne Stress-Engineering.                                                                                                             | 16 |

| 17 | Vertikale Verspannung mit Stress-Engineering.                                                                                                              | 16 |

| 18 | Laterale Verspannung ohne Stress-Engineering.                                                                                                              | 17 |

| 19 | Laterale Verspannung mit Stress-Engineering.                                                                                                               | 17 |

| 20 | Transferkennlinien mit und ohne Stress-Engineering bei $U_{Drain} = 1V$ .                                                                                  | 17 |

| 21 | Quotient der Drain-Ströme $\frac{\text{mit}}{\text{ohne}}$ Stress-Engineering.                                                                             | 18 |

| 22 | Faktor, um den sich Elektronen-Mobilität durch mechanische Verspannung geändert hat, ohne Stress-Engineering.                                              | 18 |

| 23 | Faktor, um den sich Elektronen-Mobilität durch mechanische Verspannung geändert hat, mit Stress-Engineering.                                               | 18 |